PhoenixMicro Training Course: "Designing with MPC5746R"

MPC57xx 32-bit MCU

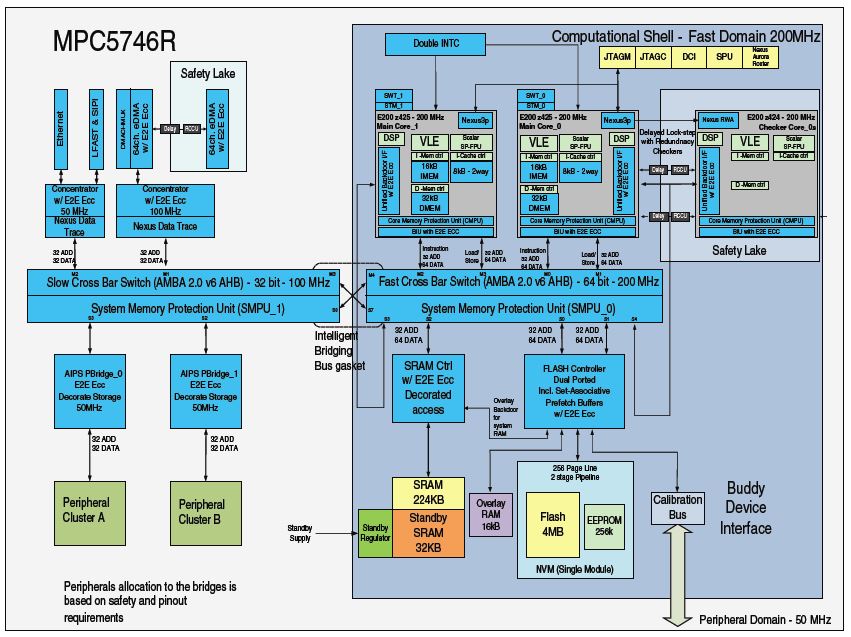

The MPC5746R Power Architecture MCU targets industrial and automotive engine/transmission control applications that require advanced performance, timing systems and functional safety capabilities. The family offers a high performance multi-core architecture with industry standard eTPU based timer system. Scalable Flash, core configurations and packaging options are available along with the highest level of functional safety (ASIL-D) support.

Audience

The MPC5746R architectural training course is designed for software, hardware, firmware, test engineers, and developers who want to build and test advanced performance automotive engine and transmission control with the high functional safety applications.

Managers, system architects, and project leaders, are also encouraged to attend the class for an in-depth understanding of the SoC device.

Course Agenda

The class will cover both the hardware and software aspect of the device. Each topic is self-contained. That is, both hardware and software materials are included to make the topic complete. The class consists of lectures and exercises.

- Architectural overview of the MPC5746R silicon systems and MPC5700 Roadmap.

- System architecture and features.

- Power Architecture programming model for the multiple e200z4 together with Variable-Length Encoding (VLE) and Light Signal Processing (LSP) Unit.

- On-chip tighly-coupled memories (TCM) including I-cache and D-cache.

- Level 2 memory organization and operation.

- Core Memory Protection Unit (CMPU) and System Memory Protection Unit (SMPU).

- Crossbar switched and bus master arbitration sequence.

- Power Architecture Exceptions and Interrupts.

- Interrupt Controller and Context Switching with new instuctions, semaphore block.

- System clock programming and PLL operation.

- Boot-Assist Flash (BAF boot sequence).

- System reset sources and reset handling.

- System initialization at start up and other device configuration with low power capabilities.

- eDMA usage and configuration.

- Various serial interface configuration such as FlexRay, DSPI, Microsecond channel (TSB), CRC generator, CAN bus, UART/LINFlexD.

- Various Memories (Flash, SRAM) and ADCs (SAR_ADCs and SD_ADC) and system timers (SWT, STM, PIT).

- More advanced timers such as enhanced Time Processor Unit (eTPU), enhanced Modular I/O Systems (eMIOS).

- In-depth understanding of Global Timer Module (GTM) with various mode of operations (TIM, TOM, ATOM) and vaious angle clock operation.

- In-depth understanding of Functinal Safety which includes two cores running in lock-step for safety integrity, Fault Control and Collection Unit (FCCU), Self-Test Control Unit (STCU2) and meeting the ASIL 26262 Standards.

- And much more...

Total topics covered will vary depending on class size, student's background, and pace of the class. Our instructors are flexible to adapt and adjust topics to suit your requirements.

Prerequisites

Understanding of basic microprocessor and microcontroller inner working are helpful. Also, familiarity with C language especially data structure organization is advantageous. However, the student willingness and desire to learn are the most important factors.

Registration

- Payment must be received no later than two weeks prior to start of course. The fee includes course note, reference manuals and applicable application notes.

- Seating is limited so please register early to get the desired place and time.

- If the student cancelled two weeks prior to course he/she can elect to have course substitution for the same course at different date.

- Student substitution is accepted from same company.

- If student did not cancel one week prior to class the student will be charge the full rate.

- PhoenixMicro Inc. has the right to cancel courses one week prior to start date due to low enrollment.