PhoenixMicro Training Course: "Designing with MPC5567 through MPC5554"

MPC55xx 32-bit MCU

The MPC55xx family, built on Power Architecture® technology, comprises 32-bit MCU devices designed for engine management, advanced driver assistance, central body, and gateway applications. The MPC55xx offers significant benefits to automotive designers, including:

- Software and hardware compatibility from low to high-end.

- Scalability among different core versions and product features.

- Builds upon embedded flash experience implemented in a high density floating-gate technology.

- Unmatched efficiency-parallel processing in conjunction with sophisticated peripheral sets.

- Leverages Power Architecture tools and software ecosystem.

Audience

The MPC5567-MPC5554 architectural training course is designed for software, hardware, firmware, test engineers, and developers who want to build and test various engine management, driver assistance, central body, and gateway applications.

Managers, system architects, and project leaders, are also encouraged to attend the class for an in-depth understanding of the SoC device.

Course Agenda

The class will cover both the hardware and software aspect of the device. Each topic is self-contained. That is, both hardware and software materials are included to make the topic complete. The class consists of lectures and exercises.

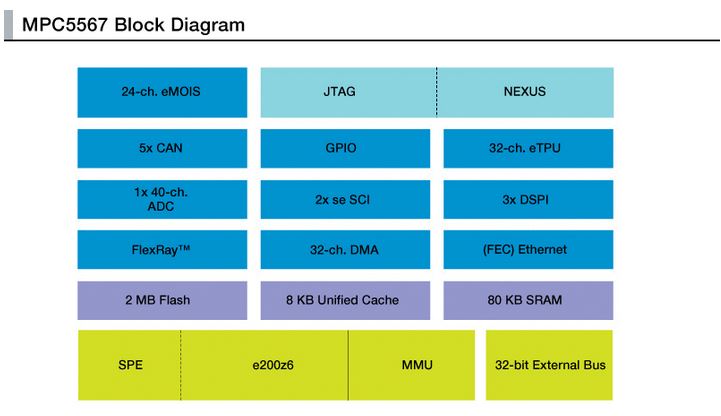

- Architectural overview of the MPC5567 and other MPC55xx derivatives.

- Learn the latest e200z6 Power Architecture Book E core programming model, register types, Signal Processing Unit (SPE), and Auxiliary Processing Unit (APE).

- Review e200z6 core instruction set, branches, subroutine calls, simplified mnemonics, including the new SIMD module for DSP and floating point features.

- Write efficient exception service routines for the e200z6 core and Interrupt Controller (INTC) by understanding the innovative exception processing function with built-in interrupt priorities, separate critical, non-critical resources using HW or SW vector mode.

- Configure and optimize the e200z6 L1 unified cache with new APU cache locking instructions.

- Initialize the improved and simplified Memory Management Unit (MMU) to perform address translation, access control, and protection.

- Configure and initialize the External Bus Interface (EBI), including memory controller, bus monitor, arbiter and various external pins needed to communicate to external peripherals.

- Understand and configure some of the enhanced TPU (eTPU) timing functions with new and easy C-like instructions. The eTPU enables more sophisticated timing functions and simplify angle domain scheduling using its powerful angle clock hardware.

- Learn how to initialize the enhanced MIOS (eMIOS) for various timer modes to drive actuators, motors, and monitor input signals.

- Configure and initialize the enhanced DMA (eDMA) to transfer data between on-chip I/O peripherals and on-chip memory via the crossbar switch (XBAR). eDMA module does not have external pins.

- Configure and initialized the enhanced QADC (eQADC) to measure analog signals using various scan modes, various trigger mechanisms, various interrupt schemes, and various digital data formats. Two independent ADCs with 12-bit A/D resolution.

- Initialize and configure the EBI to interface to external memories, I/O peripherals, ASIC or FPGA devices.

- Configure and initialize the enhanced SCI (eSCI) to perform serial communication using full-duplex/half-duplex, standard/non-standard baud rates, error checking with LIN and DMA supports.

- Configure and initialize the popular FlexCAN a serial communication protocols used for automotive and industrial control applications.

- Learn how to initialize the MPC55xx from power-on reset. Understand and use the Boot Assist Module (BAM) for device operation after reset, but before user application.

- Understand and configure the MPC55xx Fast Ethernet Controller designed to support both 10 and 100Mbps Ethernet/IEEE 802.3 networks. The FEC has a built-inFIFO and DMA controller.

- Understand and learn the MPC55xx FlexRay controller module that is compliant with the FlexRay Communications System Protocol Specification Version 2.1 and FlexRay Communications System Electrical Physical Layer Specification

Total topics covered will vary depending on class size, student's background, and pace of the class. Our instructors are flexible to adapt and adjust topics to suit your requirements.

Prerequisites

Understanding of basic microprocessor and microcontroller inner working are helpful. Also, familiarity with C language especially data structure organization is advantageous. However, the student willingness and desire to learn are the most important factors.

Registration

- Payment must be received no later than two weeks prior to start of course. The fee includes course note, reference manuals and applicable application notes.

- Seating is limited so please register early to get the desired place and time.

- If the student cancelled two weeks prior to course he/she can elect to have course substitution for the same course at different date.

- Student substitution is accepted from same company.

- If student did not cancel one week prior to class the student will be charge the full rate.

- PhoenixMicro Inc. has the right to cancel courses one week prior to start date due to low enrollment.