PhoenixMicro Training Course: "Designing with P5020 and P5010

QorIQ Platforms

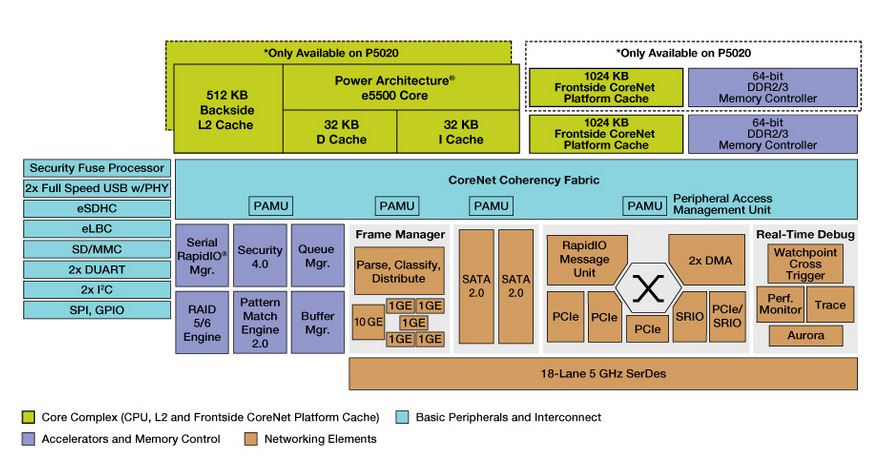

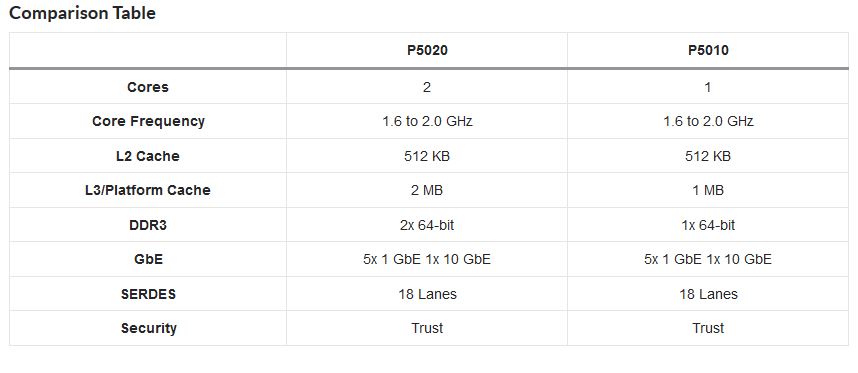

The dual-core P5020 and single-core P5010 processors deliver 64-bit processing, based on the e5500 core built on Power Architecture technology. With frequencies scalable to 2.0 GHz, large caches and high per-cycle efficiency, these products target control plane and compute applications that require high single-threaded performance.

The P5 platform leverages architectural features pioneered in the P4 platform, including the three-level cache hierarchy for low latencies, hardware hypervisor for robust virtualization support, data path acceleration architecture (DPAA) for offloading packet handling tasks from the core and the CoreNet switch fabric that eliminates internal bottlenecks. This enables architectural compatibility from the P5 platform to the P4 platform as well as to the P3 platform.

Products P5010NSE1QMB, P5010NSE1TNB, P5010NSE1VNB, P5010NSE7MMB, P5010NSE7QMB, P5010NSE7TNB, P5010NSE7VNB, P5010NSN1MMB, P5010NSN1QMB, P5010NSN1TNB, P5010NSN7MMB, P5010NSN7QMB, P5010NSN7TNB, P5010NSN7VNB, P5010NXE1QMB, P5010NXE1TNB, P5010NXE1VNB, P5010NXE7QMB, P5010NXE7TNB, P5010NXE7VNB, P5010NXN1QMB, P5010NXN1TNB, P5010NXN1VNB, P5010NXN7QMB, P5010NXN7TNB, P5010NXN7VNB, P5020NSE1QMB, P5020NSE1TNB, P5020NSE1VNB, P5020NSE7MMB, P5020NSE7QMB, P5020NSE7TNB, P5020NSE7VNB, P5020NSN1QMB, P5020NSN1VNB, P5020NSN7MMB, P5020NSN7QMB, P5020NSN7TNB, P5020NSN7VNB, P5020NXE1QMB, P5020NXE1TNB, P5020NXE7QMB, P5020NXE7TNB, P5020NXE7VNB, P5020NXN1TNB, P5020NXN1VNB, P5020NXN7QMB, P5020NXN7TNB, and P5020NXN7VNB on this page are Not Recommended for New Designs".

Audience

The P5020/P5010 architecture training course is designed for software, hardware, firmware, test engineers, and developers who want to design systems that are compute intensive, I/O intensive or both for networking, telecom, aerospace, defense and industrial markets.

Managers, system architects, and project leaders, are also encouraged to attend the class for an in-depth understanding of the SoC device.

Course Agenda

The class will cover both the hardware and software aspect of the device. Each topic is self-contained. That is, both hardware and software materials are included to make the topic complete. The class consists of lectures and exercises.

- Overview of the overall functional descriptions of the P5020 and P5010 architectures.

- Learn the latest e5500 core programming model, register types, and usages.

- Configure and optimize the L1, L2, L3 caches with new Stashing, CoreNet data intervention, Write Shadow Mode, parity generation and checking to maximize performance.

- Initialize the enhanced demand-paged virtual two-level Memory Management Unit with Hypervisor mode operations to perform address translation, access control, and protection.

- Write efficient exception service routines for the new e500mc and the Multicore Programmable Interrupt Controller (MPIC) by understanding new interrupt instructions, new interrupt features such as interrupt proxy, error reporting, new NMI, Doorbell, interrupts and multicore interrupt model.

- Learn and configure how to initialize from power-on reset, from RCW, and from Pre-Boot Loader.

- Understand the expanded internal memory map structure including Local Access Window (LAWs) and Inbound/Outbound Address Translation Mapping Units (ATMUs).

- Configure the PAMU (Peripheral Access Management Unit), which provides address translation and access control for all bus masters in the system.

- Understand the Frame Manager as it relates to Ethernet MAC controls.

- Understand and configure the DataPath Three Speed Ethernet Controller (dTSEC) for 10/100/1000 Mbps operations.

- Learn and configure the DDR2/3 SDRAM memory controllers with ECC support. Each memory controller has support for error injection for debugging and testing.

- Program the Enhanced Local Bus Controller (eLBC) using GPCM machines for static memories or peripheral devices, FCM machines for NAND Flash, and UPM machines for devices that require re-fresh.

- Configure and initialize the PCI Express 2.0 controllers with RC and EP configurations, with 32- and 64-bit address support.

- Program and initialize the 4-channel DMA controllers to transfer data between memory and Input/Output address spaces with 256 byte block transfer, externally-controlled transfer pins.

- And much more...

Total topics covered will vary depending on class size, student's background, and pace of the class. Our instructors are flexible to adapt and adjust topics to suit your requirements.

Prerequisites

Understanding of basic microprocessor and microcontroller inner working are helpful. Also, familiarity with C language especially data structure organization is advantageous. However, the student willingness and desire to learn are the most important factors.

Registration

- Payment must be received no later than two weeks prior to start of course. The fee includes course note, reference manuals and applicable application notes.

- Seating is limited so please register early to get the desired place and time.

- If the student cancelled two weeks prior to course he/she can elect to have course substitution for the same course at different date.

- Student substitution is accepted from same company.

- If student did not cancel one week prior to class the student will be charge the full rate.

- PhoenixMicro Inc. has the right to cancel courses one week prior to start date due to low enrollment.